30~45W高頻率快充應用同步整流ic U7110W

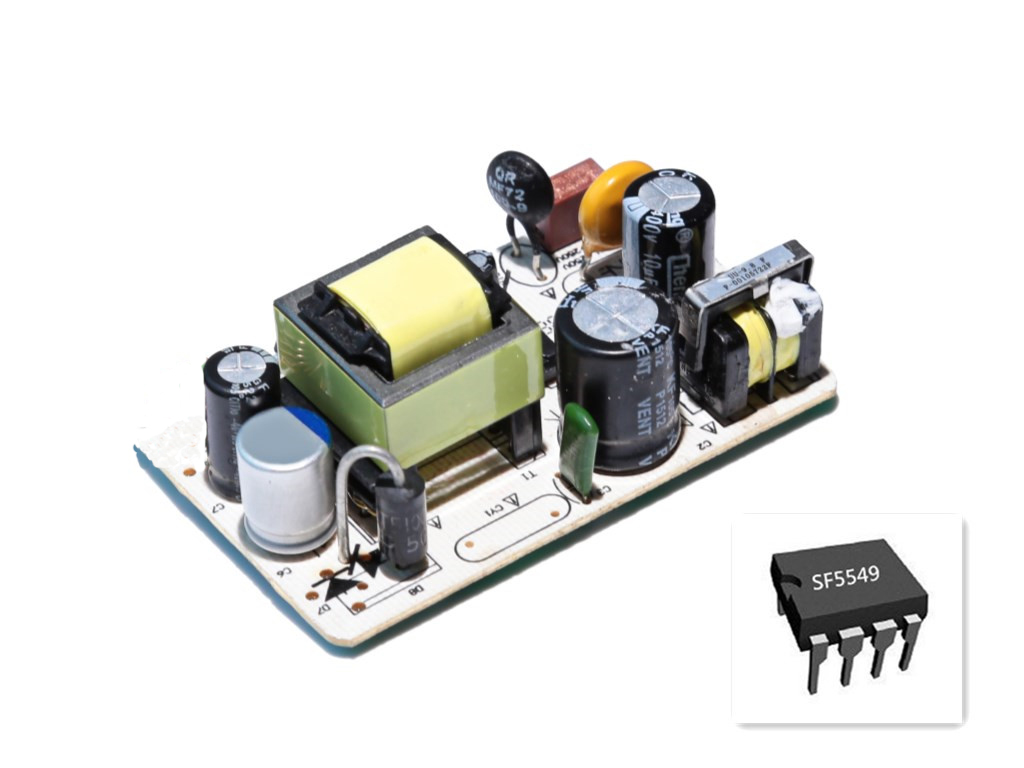

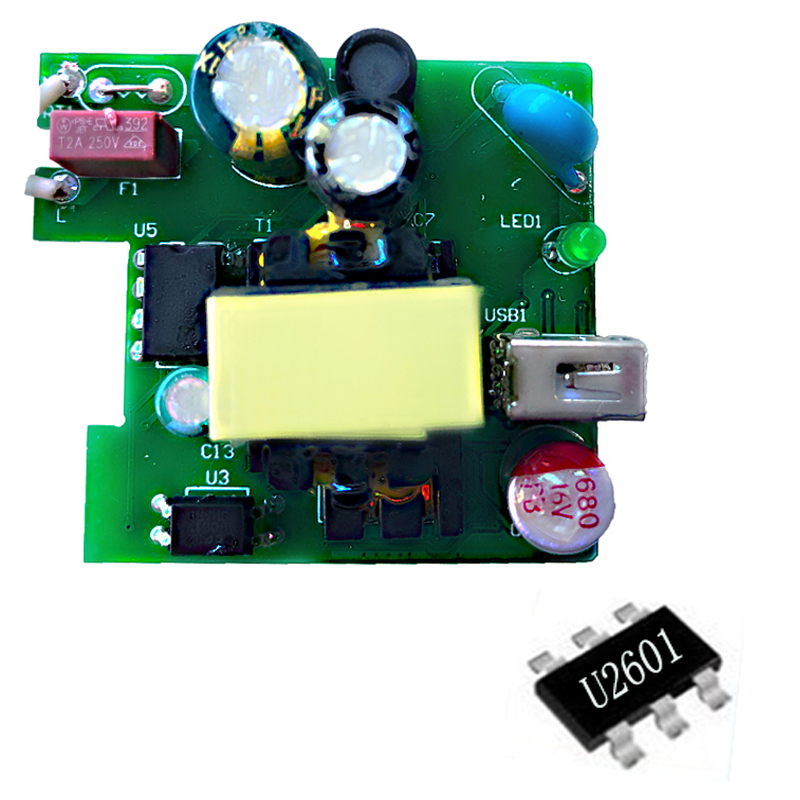

在大多數降壓調節器的典型應用中,使用有源開關而非肖特基二極管是標準做法。這樣能大大提高轉換效率,尤其是產生低輸出電壓時。在需要電流隔離的應用中,也可使用同步整流來提高轉換效率。推薦使用深圳銀聯寶最新推出的30~45W高頻率快充應用同步整流ic——U7110W!

同步整流ic U7110W是一款高頻率、高性能、CCM同步整流開關,可以在GaN系統中替代肖特基整流二極管以提高系統效率。U7110W內置有VDD高壓供電模塊,無需輔助繞組供電可穩定工作,系統上支持High Side和Low Side配置,兼顧了系統性能和成本。U7110W的快速關斷功能可以幫助功率器件獲得較低的電壓應力,可支持斷續工作模式(DCM)、準諧振工作模式(QR)及連續工作模式(CCM)。U7110W內部集成有智能的開通檢測功能,可以有效防止反激電路中寄生參數振蕩引起的同步整流開關誤開通。

PCB設計對同步整流的性能會產生顯著影響,設計同步整流電路時建議參考詳細規格書的布局設計,包含同步整流ic U7110W、變壓器副邊引腳和輸出濾波電容等。

1. 副邊主功率回路Loop1的面積盡可能小。

2. VDD電容推薦使用1μF的貼片陶瓷電容,盡量緊靠IC,Loop2的面積盡可能小。

3. HV到Drain建議串聯30~200Ω的電阻,推薦典型值100Ω。HV檢測點位置對CCM應力有影響,HV檢測點離Drain引腳越遠,CCM應力越小。High Side 配置中,建議HV通過R2電阻連接到輸出電容的正端。

4. R1和C1構成同步整流開關的RC吸收電路,RC吸收回路Loop3的面積可能小。

5. Drain 引腳的PCB散熱面積盡可能大。

6. SOP-8的封裝框架與Drain引腳電位相同,芯片切筋后,框架金屬有少量暴露,考慮到絕緣要求,外圍元器件應與IC本體保持0.2mm以上的絕緣距離。

在內置MOSFET關斷瞬間,芯片漏-源(Drain- Source)之間會產生電壓振蕩。為避免此類電壓振蕩干擾系統正常工作導致芯片誤開通,芯片內部設置了最小關斷時間(Toff_min,典型值200ns)。在Toff_min內,開通比較器被屏蔽,無法開通同步整流MOSFET,Toff_min結束后芯片再開始檢測開通條件。同步整流ic U7110W內部集成有智能開通檢測功能,可以有效防止反激電路中由于寄生參數振蕩引起的同步整流開關誤開通,提高了系統效率及可靠性。

電 話:133-1680-5165 Q Q:1957650001

電 話:133-1680-5165 Q Q:1957650001 傳 真:0755-23086550 郵 箱:001@elanpo.com

傳 真:0755-23086550 郵 箱:001@elanpo.com 地址:廣東省深圳市寶安區寶安大道4018號華豐國際商務大廈2501-2508

地址:廣東省深圳市寶安區寶安大道4018號華豐國際商務大廈2501-2508 銀聯寶手機

銀聯寶手機 招賢納士

招賢納士

主站蜘蛛池模板:

防冲撞应急处置预案|

电影1921|

睡衣派对|

黄明昊身高|

赤牙×柒cp|

红色一号电影|

五猖会原文加批注图片|

87版七仙女台湾|

拔萝卜视频免费播放|

抖音app下载|

少年圆鱼洲 综艺|

极度猎杀|

意大利诱惑|

闲章内容大全图片|

se网|

黄金城电影在线观看免费高清|

吸痰护理ppt课件|

葛思然|

殷亭如|

狼来了电影免费观看|

致爱丽丝钢琴简谱双手完整版|

男操女视频免费|

春意视频|

伊藤步|

实验室火灾报警电铃响时应当|

操蛋视频|

键|

秀场视频高清完整版|

孙嘉欣|

抖音国际版|

宁波电视台|

飞扬的青春 电视剧|

安渡|

陈学冬颖儿主演电视剧《解密》|

詹姆斯怀特|

吴朋奉|

电影交换|

国庆节安全公约|

三年片大全电影|

舞法天女第三季|

拾贝的小女孩阅读理解答案|

主站蜘蛛池模板:

防冲撞应急处置预案|

电影1921|

睡衣派对|

黄明昊身高|

赤牙×柒cp|

红色一号电影|

五猖会原文加批注图片|

87版七仙女台湾|

拔萝卜视频免费播放|

抖音app下载|

少年圆鱼洲 综艺|

极度猎杀|

意大利诱惑|

闲章内容大全图片|

se网|

黄金城电影在线观看免费高清|

吸痰护理ppt课件|

葛思然|

殷亭如|

狼来了电影免费观看|

致爱丽丝钢琴简谱双手完整版|

男操女视频免费|

春意视频|

伊藤步|

实验室火灾报警电铃响时应当|

操蛋视频|

键|

秀场视频高清完整版|

孙嘉欣|

抖音国际版|

宁波电视台|

飞扬的青春 电视剧|

安渡|

陈学冬颖儿主演电视剧《解密》|

詹姆斯怀特|

吴朋奉|

电影交换|

国庆节安全公约|

三年片大全电影|

舞法天女第三季|

拾贝的小女孩阅读理解答案|